# ACS APPLIED MATERIALS & INTERFACES

# Voltage-Controlled Ring Oscillators Based on Inkjet Printed Carbon Nanotubes and Zinc Tin Oxide

Bongjun Kim,<sup>†,‡</sup> Jaeyoung Park,<sup>‡</sup> Michael L. Geier,<sup>§</sup> Mark C. Hersam,<sup>§</sup> and Ananth Dodabalapur<sup>\*,†,‡</sup>

<sup>†</sup>Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States

<sup>‡</sup>Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, United States

<sup>§</sup>Department of Materials Science and Engineering and Department of Chemistry, Northwestern University, Evanston, Illinois 60208, United States

Supporting Information

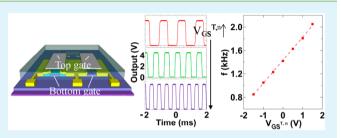

**ABSTRACT:** A voltage-controlled ring oscillator is implemented with double-gate complementary transistors where both the n- and p-channel semiconductors are deposited by inkjet printing. Top gates added to transistors in conventional ring oscillator circuits control not only threshold voltages of the constituent transistors but also the oscillation frequencies of the ring oscillators. The oscillation frequency increases or decreases linearly with applied top gate potential. The field-effect transistor materials system that yields such linear behavior has not been

previously reported. In this work, we demonstrate details of a material system (gate insulator, p- and n-channel semiconductors) that results in very linear frequency changes with control gate potential. Our use of a double layer top dielectric consisting of a combination of solution processed P(VDF-TrFE) and  $Al_2O_3$  deposited by atomic layer deposition leads to low operating voltages and near-optimal device characteristics from a circuit standpoint. Such functional blocks will enable the realization of printed voltage-controlled oscillator-based analog-to-digital converters.

**KEYWORDS:** printed electronics, thin-film transistor, carbon nanotube, zinc tin oxide, double-gate, threshold voltage, voltage-controlled oscillator

# INTRODUCTION

One of the important application area for printed electronics is in sensor systems.<sup>1,2</sup> In such systems, shown schematically as a block diagram in Figure 1, typically weak signals from a

Figure 1. Schematic block diagram of a sensor system.

sensor are first amplified and then converted to digital form before being transmitted to external electronics. Thus, analog-to-digital signal conversion is a key functional block for printed electronics. Voltage-controlled oscillators (VCOs) are key components of VCO-based analog-to-digital converters (ADCs).<sup>3,4</sup> There have been a few reports on organictransistor-based ADCs;<sup>5–9</sup> however, most of these were not based on printed semiconductors. In this paper, we report the realization of voltage-controlled double-gate complementary ring oscillators (ROSCs) utilizing inkjet printed semicon-ductors.

Numerous semiconductor and dielectric material systems are being investigated for printed electronics. Semiconductor materials such as polymers, amorphous oxides, and singlewalled carbon nanotubes (SWCNTs) have been demonstrated in printed electronics with each material possessing advantages and drawbacks for specific applications.<sup>10–15</sup> In previous work, we demonstrated complementary circuits with inkjet printed p-channel SWCNT thin-film transistors (TFTs) and n-channel amorphous oxide TFTs as foundational elements for printed electronics.<sup>16,17</sup> In this paper, we show that the addition of double-gate functionality yields VCOs that are more easily implemented with printed transistors compared to traditional designs based on analog components such as operational amplifiers. Frequency tuning characteristics of double-gate ROSCs with a pentacene active layer have been previously reported.<sup>18,19</sup> However, their use in ADCs and the linearity of tuning characteristics have not received adequate attention and can be improved by using different semiconductors. The response of an ADC is governed by its bandwidth that is

```

Received:

March 9, 2015

Accepted:

May 12, 2015

Published:

May 12, 2015

```

ACS Publications © 2015 American Chemical Society

## **ACS Applied Materials & Interfaces**

determined by the sampling rate. For systems such as those depicted in Figure 1, it is not necessary to implement a full ADC at the site of a sensor; rather, the focus should be on keeping the sampling rate as high as possible. This goal is best achieved with voltage-controlled ring oscillators (VCROs) that possess higher oscillation frequencies than the clock frequency of the corresponding digital circuits. Thus, a scheme in which the analog signal is converted to a frequency modulated square wave will efficiently propagate the signal from the sensor to the control electronics, where additional processing can be performed. Adding a buffer amplifier (i.e., two inverters in series) will improve the pulse shape of the VCO output, if required.

## EXPERIMENTAL SECTION

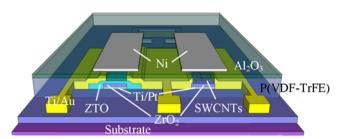

Device Fabrication. The bottom gate electrodes, which consist of patterned e-beam evaporated Ti/Pt bilayers (3 nm/30 nm), were formed on Si/SiO<sub>2</sub> substrates by photolithography, followed by lift-off. The bottom gate dielectric layer, ZrO2, was deposited by a sol-gel route. Via holes to the bottom gate electrodes were patterned by photolithography and reactive ion etching (CHF<sub>3</sub>/O<sub>2</sub> at a pressure of 40 mTorr). The n-type active layer, zinc tin oxide (ZTO), was deposited by sequential inkjet printing three times, after UV O<sub>3</sub> surface treatment for 10 min. After ZTO printing, the substrate was annealed on a hot plate at 500 °C for 1 h in air. The p-type active layer, SWCNTs (>98% semiconducting purity prepared by den-sity gradient ultracentrifugation),<sup>20,21</sup> was deposited by inkjet printing, after UV O<sub>3</sub> surface treatment for 10 min. After printing the SWCNTs, the substrate was placed on a hot plate at 200 °C for 30 min in air to remove residual solvents. More details on the preparation of  $\rm ZrO_2$ , ZTO, and SWCNT solutions and the printing conditions are described in our previous papers.^{16,22-24} The source/ drain (S/D) electrodes were patterned by photolithography, and Ti/Au (3.5 nm/20 nm) was deposited by thermal evaporation, followed by lift-off.

Poly(vinylidene fluoride-trifluoroethylene) (P(VDF-TrFE)) (Solvay Solexis Inc., 75/25 mol %) solution, dissolved in diethyl carbonate (25 mg/mL), was spin-coated on top of the devices at a spin speed of 2000 rpm for 45 s. The substrate was baked on a hot plate at 140 °C for 3 min in air to remove solvents. A thin  $Al_2O_3$  layer (12.5 nm) was deposited on top of the P(VDF-TrFE) layer by atomic layer deposition (ALD) at 80 °C. After  $Al_2O_3$  deposition, the top gate dielectrics on the contact pads were removed with acetone. Finally, Ni (50 nm) was deposited by thermal evaporation through a shadow mask to form the top gate electrodes.<sup>25</sup>

**Electrical Characterization of Devices.** All measurements were performed under ambient conditions. The characteristics of TFTs and inverters were measured using a HP 4155C semiconductor parameter analyzer. For the ROSC measurement, the output signals were measured with a LeCroy WaveRunner 6030 oscilloscope, and other voltages were supplied by the HP4155C.

## RESULTS AND DISCUSSION

Figure 2 illustrates a schematic structure of the double-gate complementary inverter based on inkjet printed SWCNTs and ZTO. The top gate dielectric for these devices consists of a bilayer of P(VDF-TrFE) and  $Al_2O_3$ . The P(VDF-TrFE) layer has been shown in previous work to mitigate the effects of charged defects in the p-channel SWCNTs, leading to significantly improved electrical characteristics.<sup>26</sup> A thin  $Al_2O_3$  layer was deposited on top of the P(VDF-TrFE) to reduce gate leakage current and improve the overall gate dielectric stack performance.

The threshold voltage  $(V_{\rm th})$  of the TFTs in a double-gate structure can be controlled by the potential applied to either the bottom or top gates.<sup>27–31</sup> In this work, bottom gates were

Figure 2. Schematic structure of a double-gate complementary inverter based on inkjet printed SWCNTs and ZTO.

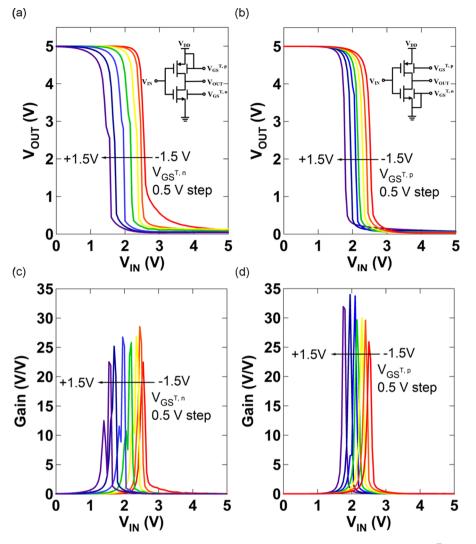

**Figure 3.** (a) Transfer characteristics of the double-gate ZTO TFT at various n-TFT top-gate-source voltages  $(V_{\text{GS}}^{\text{T,n}})$ . (b) Transfer characteristics of the double-gate SWCNT TFT at various p-TFT top-gate-source voltages  $(V_{\text{GS}}^{\text{T,p}})$ . (c) Output characteristics of the double-gate SWCNT (left) and ZTO (right) TFTs at  $V_{\text{GS}}^{\text{T}} = 1.5$  V and at (d)  $V_{\text{GS}}^{\text{T}} = -1.5$  V.

employed as conventional gates (as in single gate TFTs) because the bottom gate dielectric exhibits a higher capacitance value  $(148 \text{ nF cm}^{-2})^{16}$  than that of the top gate dielectric (~106 nF cm<sup>-2</sup>) (Supporting Information, Figure S1), while the top gates were employed as the control gates. Figure 3a, b shows transfer characteristics of the double-gate TFTs in linear mode ( $|V_{DS}| = 0.5$  V). Both ZTO and SWCNT TFTs possess the same channel length (*L*) = 20  $\mu$ m and channel width (*W*) = 400  $\mu$ m. The ZTO TFT exhibits linear field-effect mobility of 0.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and an  $I_{on}/I_{off}$  ratio of 8.5 × 10<sup>2</sup>, while the SWCNT TFT exhibits linear field-effect mobility of 0.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and an  $I_{\rm on}/I_{\rm off}$  ratio of 6.2  $\times$  10<sup>3</sup>, when the n-TFT top-gate-source voltage  $(V_{\rm GS}^{\rm T,n})$  and the p-TFT top-gate-source voltage  $(V_{\rm GS}^{\rm T,p})$  are 0 V and  $|V_{\rm DS}|$ = 0.5 V. In the case of the ZTO TFT,  $V_{\rm th}$  shifts toward more negative voltage, and  $I_{\rm on}$  increases when  $V_{\rm GS}^{\rm T,n}$  increases. In the case of the SWCNT TFT,  $V_{\rm th}$ shifts toward more positive voltage, and  $|I_{op}|$  increases when  $V_{GS}^{T,p}$  decreases. Figure 3c, d shows output characteristics of

**Figure 4.** (a) Voltage transfer characteristics (VTCs) of the double-gate complementary inverter as a function of  $V_{GS}^{T,n}$  and (inset) the top gate of p-TFT connected to the source ( $V_{DD}$ ) of p-TFT. (b) VTCs of the double-gate complementary inverter as a function of  $V_{GS}^{T,p}$  and (inset) the top gate of n-TFT connected to the source (GND) of n-TFT. (c) DC gains ( $|dV_{out}/dV_{in}|$ ) of the inverter as a function of  $V_{GS}^{T,n}$ . (d) DC gains of the inverter as a function of  $V_{GS}^{T,p}$ .

the double-gate TFTs at both  $V_{\rm GS}{}^{\rm T,p}$  and  $V_{\rm GS}{}^{\rm T,n} = 1.5$  V and at both  $V_{\rm GS}{}^{\rm T,p}$  and  $V_{\rm GS}{}^{\rm T,n} = -1.5$  V, respectively.  $I_{\rm DS}$  varies depending on  $V_{\rm GS}{}^{\rm T}$  for both TFTs; however, the difference in  $I_{\rm DS}$  between when  $V_{\rm GS}{}^{\rm T} = 1.5$  V and  $V_{\rm GS}{}^{\rm T} = -1.5$  V is smaller in the SWCNT TFT compared to in the ZTO TFT. This difference can be attributed to the lower gate modulation of the SWCNT TFT in the saturation regime (Supporting Information, Figure S2). A possible reason for this is that the top gate dielectric stack is thicker for SWCNT TFTs compared to ZTO TFTs.

A complementary inverter was constructed by connecting double-gate SWCNT (p-channel) and ZTO (n-channel) TFTs as illustrated in Figure 2 and the insets of Figure 4a, b. The inverter was characterized by applying  $V_{\rm GS}^{\rm T}$  to either the top gate of the p-TFT or n-TFT, while the other top gate was connected to its source. Input voltages ( $V_{\rm IN}$ ) were applied to the connected bottom gate. Figure 4a shows voltage transfer characteristics of the inverter at different values of  $V_{\rm GS}^{\rm T,n}$ , where the curve shifts to the left along the axis of  $V_{\rm IN}$  when  $V_{\rm GS}^{\rm T,n}$  increases. This shift occurs because  $I_{\rm DS}$  of the n-TFT increases with the increase of  $V_{\rm GS}^{\rm T,n}$ , while  $I_{\rm DS}$  of

the p-TFT remains the same. The DC gains  $(|dV_{out}/dV_{in}|)$  of the inverter at different  $V_{GS}^{T,n}$  are shown in Figure 4c. The maximum gain point also shifts to the left when  $V_{GS}^{T,n}$ increases. These shifts are observed similarly when  $V_{GS}^{T,p}$ increases (Figure 4b, d). In this case,  $|I_{DS}|$  of the p-TFT decreases with the increase of  $V_{GS}^{T,p}$ , while  $I_{DS}$  of the n-TFT remains the same. However, the shifts are less in magnitude in the SWCNT TFT case for the reason mentioned above.

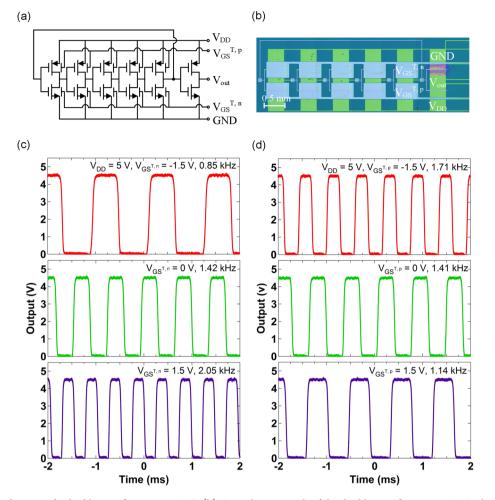

The double-gate  $V_{\rm th}$  tuning characteristics can be applied to ROSC circuits to control their oscillation frequencies. For example, five double-gate inverters were connected in a loop to construct a five-stage double-gate ROSC with a buffer stage as shown in Figure 5a. Figure 5b shows an optical micrograph of the ROSC. All TFTs in the ROSC circuit possess the same channel dimensions ( $L = 20 \ \mu m$ ;  $W = 400 \ \mu m$ ). Figure 5c, d shows output signals of the ROSC at three different values of  $V_{\rm GS}^{\rm T,n}$  and  $V_{\rm GS}^{\rm T,p}$ , respectively, resulting in a frequency modulation of the ROSC. In particular, the oscillation frequency of the ROSC increases as  $V_{\rm GS}^{\rm T,n}$  increases (Figure 5c). In contrast, the oscillation frequency of the ROSC decreases as  $V_{\rm GS}^{\rm T,p}$  increases (Figure 5d).

**Figure 5.** (a) Circuit diagram of a double-gate five-stage ROSC. (b) Optical micrograph of the double-gate five-stage ROSC; the upper six TFTs are ZTO (n-channel) TFTs, and the lower six TFTs are SWCNT (p-channel) TFTs. (c) Output signals of the double-gate ROSC at different values of  $V_{GS}^{T,n}$  and (d) at different values of  $V_{GS}^{T,p}$ .

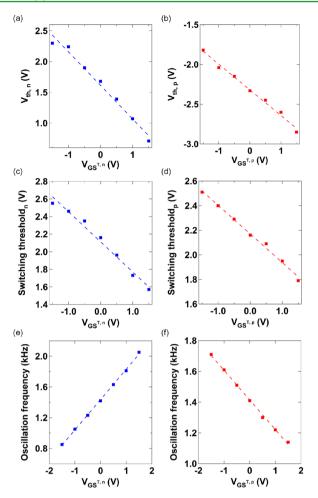

Figure 6 shows summarized tuning characteristics of the top gate potentials on TFTs, inverters, and ROSCs. Figure 6a shows the  $V_{\rm th}$  tuning characteristics of the ZTO TFT by applying different values of  $V_{\rm GS}{}^{\rm T,n}$ , and Figure 6b shows the  $V_{\rm th}$  tuning characteristics of the SWCNT TFT by applying different values of  $V_{\rm GS}{}^{\rm T,p}$ . The switching threshold of the inverter, where  $V_{\rm IN} = V_{\rm OUT}$ , decreases when  $V_{\rm GS}{}^{\rm T,n}$  and  $V_{\rm GS}{}^{\rm T,p}$  increase (Figure 6c, d).

The frequency of the ROSC increases linearly as  $V_{\rm GS}^{\rm T,n}$  increases (Figure 6e), while the frequency decreases linearly as  $V_{\rm GS}^{\rm T,p}$  increases (Figure 6f). Quantitatively, linear fitting curves almost exactly match the measured data points ( $R^2 = 0.999$  in Figure 6e;  $R^2 = 0.997$  in Figure 6f). This linearity is expected from the basic equation (eq 1) that describes the oscillation frequency in a CMOS-based ROSC:<sup>32</sup>

$$f \propto \frac{1}{NR_{\rm on}C} \propto V_{\rm ov} \tag{1}$$

where *N* is the number of stages,  $R_{on}$  is the on-resistance, *C* is the capacitance, and  $V_{ov}$  is the overdrive voltage ( $V_{ov} = V_{GS} - V_{th}$ ). However, for TFTs with disordered semiconductors,  $R_{on}$  in eq 1 will change nonlinearly with the gate potential because of the dependence of mobility on carrier density. The capacitance, *C*, in eq 1 will also change in the opposite direction with the gate potential due to charge storage. The combined effect of both these changes results in a substantially linear oscillation frequency versus gate potential characteristic that we observe as shown in Figure 6e, f. Such a linear characteristic will result in minimal distortion of the analog signal. The frequency modulated square wave output of the VCRO will have a higher bandwidth (and hence sampling rate) compared to a conventional ADC,<sup>5–7</sup> in which the slow clock speeds of the organic- or printed-electronics-based digital electronics will limit performance. This improvement occurs because the oscillation frequencies of ROSCs are typically much higher than the clock frequencies of flip-flops or other digital components for any given technology.

## CONCLUSION

A VCRO has been demonstrated by employing a double-gate structure where the active semiconductors of the circuits are deposited by inkjet printing. Threshold voltages in individual TFTs, switching thresholds in complementary inverters, and oscillation frequencies in ROSCs are systemically controlled by applying top-gate-source voltages in double-gated devices. A key requirement for the VCO, linearity between frequencies and voltages, has been achieved by simply adding a top gate dielectric and top gates on top of conventional ROSCs in place of more complex circuit designs. Consequently, the circuits demonstrated here are

**Figure 6.** (a) Threshold voltage shift of the ZTO TFT as a function of  $V_{\rm GS}^{\rm T,n}$ . (b) Threshold voltage shift of the SWCNT TFT as a function of  $V_{\rm GS}^{\rm T,p}$ . (c) Switching threshold shifts of the inverter as a function of  $V_{\rm GS}^{\rm T,n}$ . (d) Switching threshold shifts of the inverter as a function of  $V_{\rm GS}^{\rm T,p}$ . (e) Oscillation frequencies of the double-gate ROSC as a function of  $V_{\rm GS}^{\rm T,p}$  at  $V_{\rm DD} = 5$  V. (f) Oscillation frequencies of the double-gate ROSC as a function of  $V_{\rm GS}^{\rm T,p}$  at  $V_{\rm DD} = 5$  V. Dotted lines in a–e show linear fitting of the measured data (shown in squares).

likely to accelerate efforts to realize printed-electronics-based signal processing in distributed sensors and related technologies.

## ASSOCIATED CONTENT

#### **S** Supporting Information

Capacitance of a bilayer of  $P(VDF-TrFE)/Al_2O_3$ ; transfer characteristics of SWCNT and ZTO TFTs in the saturation regime; SPICE simulation results of double-gate inverters; propagation delay per stage of the double-gate ROSC as a function of top gate-source voltages. The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.5b02093.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: ananth.dodabalapur@engr.utexas.edu.

### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

The authors acknowledge financial support from the Office of Naval Research MURI grant no. N00014-11-1-0690. A National Science Foundation Graduate Research Fellowship (M.L.G.) is also acknowledged. B.K. thanks the Kwanjeong Educational Foundation for support. The authors thank Seonpil Jang and Craig Milroy at The University of Texas at Austin for their assistance on preparation of the P(VDF-TrFE) solution. The authors also thank Prof. T. R. Viswanathan, Rohit Yadav, and Yeonam Yoon at The University of Texas at Austin for helpful discussions.

## REFERENCES

(1) Someya, T.; Sekitani, T.; Iba, S.; Kato, Y.; Kawaguchi, H.; Sakurai, T.; Whitesides, G. M. A Large-Area, Flexible Pressure Sensor Matrix with Organic Field-Effect Transistors for Artificial Skin Applications. *Proc. Natl. Acad. Sci. U.S.A.* **2004**, *101*, 9966–9970.

(2) Rogers, J. A.; Someya, T.; Huang, Y. Materials and Mechanics for Stretchable Electronics. *Science* **2010**, *327*, 1603–1607.

(3) Straayer, M. Z.; Perrott, M. H. A 12-Bit, 10-MHz Bandwidth, Continuous-Time  $\Sigma\Delta$ ADCWith a 5-Bit, 950-MS/s VCO-Based Quantizer. *IEEE J. Solid-State Circuits* **2008**, 43, 805–814.

(4) Kim, J.; Jang, T.-K.; Yoon, Y.-G.; Cho, S. Analysis and Design of Voltage-Controlled Oscillator Based Analog-to-Digital Converter. *IEEE Trans. Circuits Syst.* **2010**, *57*, 18–30.

(5) Wei, X.; Zschieschang, U.; Klauk, H.; Murmann, B. A 3V 6b Successive-Approximation ADC Using Complementary Organic Thin-Film Transistors on Glass. *IEEE ISSCC Dig. Tech. Pap.* **2010**, 134–135.

(6) Marien, H.; Steyaert, M. S. J.; van Veenendaal, E.; Heremans, P. A Fully Integrated  $\Delta\Sigma$  ADC in Organic Thin-Film Transistor Technology on Flexible Plastic Foil. *IEEE J. Solid-State Circuits* **2011**, 46, 276–284.

(7) Abdinia, S.; Benwadih, M.; Coppard, R.; Jacob, S.; Maiellaro, G.; Palmisano, G.; Rizzo, M.; Scuderi, A.; Tramontana, F.; van Roermund, A.; Cantatore, E. A 4b ADC Manufactured in a Fully-Printed Organic Complementary Technology Including Resistors. *IEEE ISSCC Dig. Tech. Pap.* **2013**, 106–107.

(8) Raiteri, D.; van Lieshout, P.; van Roermund, A.; Cantatore, E. An Organic VCO-Based ADC for Quasi-static Signals Achieving 1LSB INL at 6b Resolution. *IEEE ISSCC Dig. Tech. Pap.* **2013**, 108–109.

(9) Ganesan, R.; Krumm, J.; Ludwig, K.; Glesner, M. Investigation of Voltage-Controlled Oscillator Circuits Using Organic Thin-Film Transistors (OTFT) for Use in VCO-Based Analog-to-Digital Converters. *Solid-State Electron.* **2014**, *93*, 8–14.

(10) Lee, D.-H.; Chang, Y.-J.; Herman, G. S.; Chang, C.-H. A General Route to Printable High-Mobility Transparent Amorphous Oxide Semiconductors. *Adv. Mater.* **2007**, *19*, 843–847.

(11) Lee, S. H.; Choi, M. H.; Han, S. H.; Choo, D. J.; Jang, J.; Kwon, S. K. High-Performance Thin-Film Transistor with 6,13-Bis-(triisopropylsilylethynyl) Pentacene by Inkjet Printing. *Org. Electron.* **2008**, *9*, 721–726.

(12) Ha, M.; Xia, Y.; Green, A. A.; Zhang, W.; Renn, M. J.; Kim, C. H.; Hersam, M. C.; Frisbie, C. D. Printed, Sub-3V Digital Circuits on Plastic from Aqueous Carbon Nanotube Inks. *ACS Nano* **2010**, *4*, 4388–4395.

(13) Hennek, J. W.; Xia, Y.; Everaerts, K.; Hersam, M. C.; Facchetti, A.; Marks, T. J. Reduced Contact Resistance in Inkjet Printed High-Performance Amorphous Indium Gallium Zinc Oxide Transistors. *ACS Appl. Mater. Interfaces* **2012**, *4*, 1614–1619.

(14) Chung, S.; Jang, M.; Ji, S.-B.; Im, H.; Seong, N.; Ha, J.; Kwon, S.-K.; Kim, Y.-H.; Yang, H.; Hong, Y. Flexible High-Performance All-Inkjet-Printed Inverters: Organo-Compatible and Stable Interface Engineering. *Adv. Mater.* **2013**, *25*, 4773–4777.

(15) Lau, P. H.; Takei, K.; Wang, C.; Ju, Y.; Kim, J.; Yu, Z.; Takahashi, T.; Cho, G.; Javey, A. Fully Printed, High Performance

## **ACS Applied Materials & Interfaces**

Carbon Nanotube Thin-Film Transistors on Flexible Substrates. *Nano Lett.* 2013, 13, 3864–3869.

(16) Kim, B.; Jang, S.; Geier, M. L.; Prabhumirashi, P. L.; Hersam, M. C.; Dodabalapur, A. High-Speed, Inkjet-Printed Carbon Nanotube/ Zinc Tin Oxide Hybrid Complementary Ring Oscillators. *Nano Lett.* **2014**, *14*, 3683–3687.

(17) Kim, B.; Geier, M. L.; Hersam, M. C.; Dodabalapur, A. Complementary D Flip-Flops Based on Inkjet Printed Single-Walled Carbon Nanotubes and Zinc Tin Oxide. *IEEE Electron Device Lett.* **2014**, *35*, 1245–1247.

(18) Takamiya, M.; Sekitani, T.; Kato, Y.; Kawaguchi, H.; Someya, T.; Sakurai, T. An Organic FET SRAM with Back Gate to Increase Static Noise Margin and Its Application to Braille Sheet Display. *IEEE J. Solid-State Circuits* **2007**, *42*, 93–100.

(19) Myny, K.; Beenhakkers, M. J.; van Aerle, N. A. J. M.; Gelinck, G. H.; Genoe, J.; Dehaene, W.; Heremans, P. Unipolar Organic Transistor Circuits Made Robust by Dual-Gate Technology. *IEEE J. Solid-State Circuits* **2011**, *46*, 1223–1230.

(20) Arnold, M. S.; Green, A. A.; Hulvat, J. F.; Stupp, S. I.; Hersam, M. C. Sorting Carbon Nanotubes by Electronic Structure Using Density Differentiation. *Nat. Nanotechnol.* **2006**, *1*, 60–65.

(21) Green, A. A.; Hersam, M. C. Nearly Single-Chirality Single-Walled Carbon Nanotubes Produced via Orthogonal Iterative Density Gradient Ultracentrifugation. *Adv. Mater.* **2011**, *23*, 2185–2190.

(22) Lee, C.-G.; Dodabalapur, A. Solution-Processed Zinc-Tin Oxide Thin-Film Transistors with Low Interfacial Trap Density and Improved Performance. *Appl. Phys. Lett.* **2010**, *96*, 243501.

(23) Kim, B.; Jang, S.; Prabhumirashi, P. L.; Geier, M. L.; Hersam, M. C.; Dodabalapur, A. Low Voltage, High Performance Inkjet Printed Carbon Nanotube Transistors with Solution Processed ZrO<sub>2</sub> Gate Insulator. *Appl. Phys. Lett.* **2013**, *103*, 082119.

(24) Kim, B.; Jang, S.; Geier, M. L.; Prabhumirashi, P. L.; Hersam, M. C.; Dodabalapur, A. Inkjet Printed Ambipolar Transistors and Inverters Based on Carbon Nanotube/Zinc Tin Oxide Heterostructures. *Appl. Phys. Lett.* **2014**, *104*, 062101.

(25) Geier, M. L.; Prabhumirashi, P. L.; McMorrow, J. J.; Xu, W.; Seo, J.-W. T.; Everaerts, K.; Kim, C. H.; Marks, T. J.; Hersam, M. C. Subnanowatt Carbon Nanotube Complementary Logic Enabled by Threshold Voltage Control. *Nano Lett.* **2013**, *13*, 4810–4814.

(26) Jang, S.; Kim, B.; Geier, M. L.; Prabhumirashi, P. L.; Hersam, M. C.; Dodabalapur, A. Fluoropolymer Coatings for Improved Carbon Nanotube Transistor Device and Circuit Performance. *Appl. Phys. Lett.* **2014**, *105*, 122107.

(27) Gelinck, G. H.; van Veenendaal, E.; Coehoorn, R. Dual-Gate Organic Thin-Film Transistors. *Appl. Phys. Lett.* **2005**, *87*, 073508.

(28) Morana, M.; Bret, G.; Brabec, C. Double-Gate Organic Field-Effect Transistor. *Appl. Phys. Lett.* 2005, 87, 153511.

(29) Hizu, K.; Sekitani, T.; Someya, T.; Otsuki, J. Reduction in Operation Voltage of Complementary Organic Thin-Film Transistor Inverter Circuits Using Double-Gate Structures. *Appl. Phys. Lett.* **200**7, *90*, 093504.

(30) Spijkman, M.-J.; Myny, K.; Smits, E. C. P.; Heremans, P.; Blom, P. W. M.; de Leeuw, D. M. Dual-Gate Thin-Film Transistors, Integrated Circuits and Sensors. *Adv. Mater.* **2011**, *23*, 3231–3242.

(31) Wang, H.; Cobb, B.; van Breemen, A.; Gelinck, G.; Bao, Z. Highly Stable Carbon Nanotube Top-Gate Transistors with Tunable Threshold Voltage. *Adv. Mater.* **2014**, *26*, 4588–4593.

(32) Drost, B.; Talegaonkar, M.; Hanumolu, P. K. Analog Filter Design Using Ring Oscillator Integrators. *IEEE J. Solid-State Circuits* **2012**, 47, 3120–3129.